DMI – Graduate Course in Computer Science

Copyleft

![]() 2020 Giuseppe Scollo

2020 Giuseppe Scollo

this tutorial deals with:

single-clock synchronous digital circuits, composed of an interconnection of:

thus also including widely used components such as: registers, adders, multiplexers etc.

what cannot be modeled: asynchronous hardware, HW with latches, multi-phase clocked HW etc.

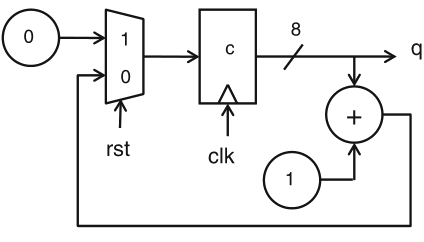

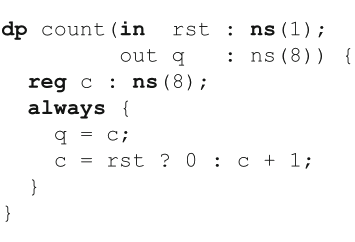

example:

Schaumont, Fig. 1.1 - Models and behaviour of a hardware component

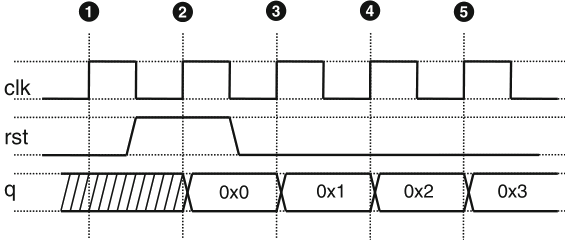

reconsider the example seen in the first lecture:

dp collatz (

in start : ns(1) ;

in x0 : ns(16) ;

out t : ns(32)) {

reg r : ns(32) ;

sig x : ns(32) ;

always {

t = r ;

x = start ? x0 : r ;

r = x[0] ? x + (x >> 1) + 1 : x >> 1 ;

}

}

what can be done with such a model?

industrial development tools need descriptions in standard languages such as VHDL or Verilog ...

the code generator of the Gezel platform yields a translation into synthesizable VHDL

lab experience:

a few tips to perform the lab experience on Ubuntu 16.04:

recommended readings:

for further consultation:

other useful material for the proposed lab experience: