DMI – Corso di laurea magistrale in Informatica

Copyleft

![]() 2019 Giuseppe Scollo

2019 Giuseppe Scollo

in questa esercitazione si affronta un caso di studio di accelerazione hardware

nella precedente esercitazione è stata presentata una realizzazione software del calcolo del delay di una traiettoria di Collatz di dato inizio

realizzazioni hardware della stessa funzione sono state oggetto di precedenti esperienze di laboratorio

le misure di prestazione condotte sulla realizzazione software mostrano che essa assorbe quasi tutto il tempo di esecuzione del programma

una prima alternativa da valutare: integrare la funzione hardware come istruzione custom o come coprocessore mappato in memoria?

altre decisioni di progetto dipendono da questa prima decisione, come segue

la descrizione VHDL del circuito di calcolo della funzione va incorporata in un componente dotato di interfacce Avalon per i segnali di Clock, Reset e di Avalon MM Slave, sì da ricevere il dato iniziale da un'operazione di scrittura e fornire il risultato in risposta a un'operazione di lettura

indirizzamento del coprocessore: poiché le operazioni di scrittura (del dato iniziale) e lettura (del risultato) avvengono in tempi diversi e hanno la stessa dimensione del dato, un solo indirizzo è sufficiente

driver software : si possono definire due macro e una funzione per l'interfaccia software di accesso al bus: DC_RESET(d), DC_START(d,x0), unsigned int delay(d), dove d è l'indirizzo assegnato al coprocessore

fasi principali di sviluppo:

due sorgenti VHDL realizzano il coprocessore memory-mapped:

entrambi i sorgenti sono disponibili nella cartella vhdl dell'archivio allegato, reperibile anche nella cartella Nios II dell'area riservata di laboratorio

la consultazione del sorgente delay_collatz_interface.vhd mostra le relazioni tra i segnali di I/O del componente di calcolo e i segnali all'interfaccia Avalon

la cartella codesign nell'archivio allegato è predisposta per ospitare lo sviluppo del progetto

creato il progetto delay_collatz_codesign, con omonima entità top-level, si procede alla creazione del componente custom delay_collatz_interface

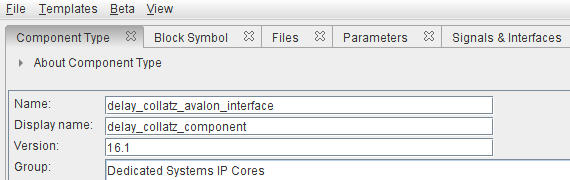

la definizione del nuovo tipo di componente è mostrata in figura

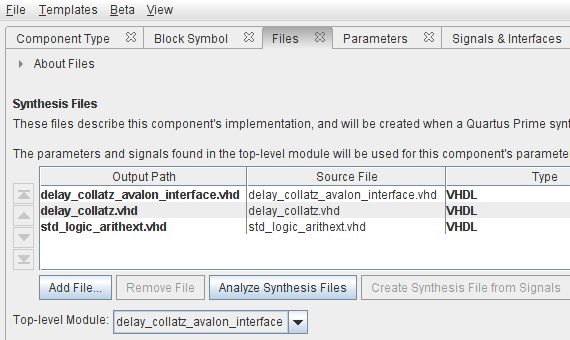

si procede quindi all'assegnazione dei file VHDL che descrivono il componente e alla loro analisi, come mostrato in figura

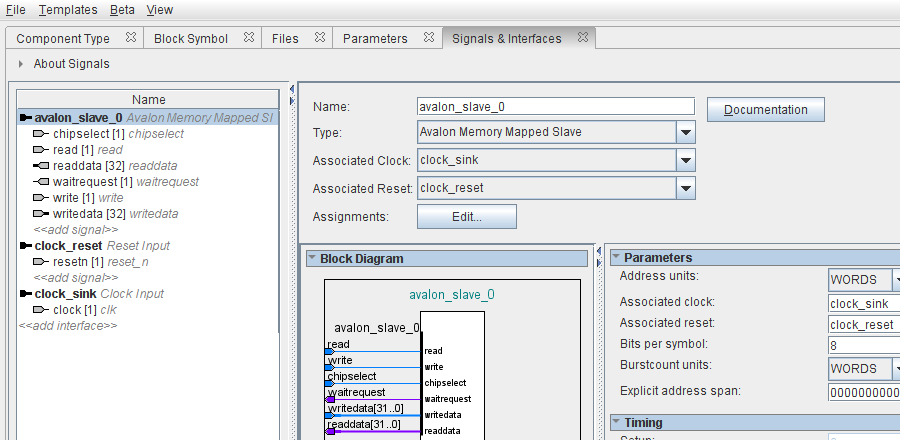

infine, si conclude la definizione del nuovo tipo di componente con la definizione delle sue interfacce Avalon e la collocazione dei segnali nelle interfacce appropriate, come illustrato in figura

per la costruzione del sistema Nios II illustrato nelle figure precedenti può essere utile la consultazione del tutorial di introduzione a Qsys

i passi finali per il mapping del sistema sulla FPGA sono i seguenti:

in Qsys:

uscire da Qsys, quindi in Quartus:

la cartella script nell'archivio allegato contiene due script TCL per la generazione del driver software nel BSP del progetto

questi script vanno copiati nella cartella codesign/ip/delay_collatz_avalon_interface

gli script TCL sono stati scritti in analogia allo script TCL del driver

software del Performance Counter, reperibile nella distribuzione del software

Quartus Prime Lite 16.1 al percorso

$SOPC_KIT_NIOS2/../ip/altera/sopc_builder_ip/altera_avalon_performance_counter

la motivazione per questo modo, forse poco ortodosso, di produzione del driver software sta nel duplice fatto che

a cui si aggiunge un discreto grado di analogia operativa dei due componenti

la cartella src nell'archivio allegato contiene i programmi in questione, da copiare nelle cartelle di creazione dei progetti di test e misura delle prestazioni mediante il Monitor Program, come segue:

i parametri di creazione dei progetti sono indicati nel file allegato MonitorNotes.txt

differenze principali tra il sorgente dell'esercitazione 10 e l'attuale versione sequenziale:

la versione pipelined del programma presenta differenze molto più marcate rispetto al programma dell'esercitazione 10:

il meccanismo di sincronizzazione è molto semplice, grazie a proprietà del componente custom e del segnale waitrequest del protocollo Avalon MM:

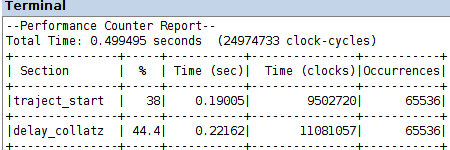

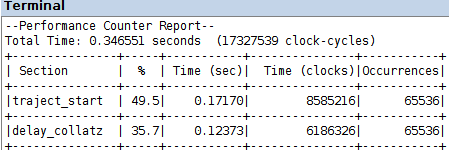

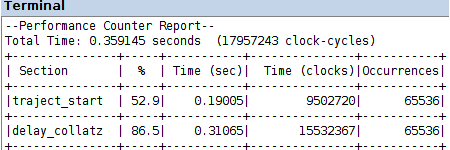

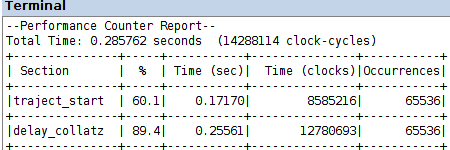

la compilazione, caricamento sulla FPGA ed esecuzione del programma delay_collatz_sequential_timing.c, nei due progetti codesign/amp_s e codesign/amp_s_o3 produce i Performance Counter Report in figura

uno speed-up di un ordine di grandezza, rispetto al calcolo software nell'esercitazione 10, risulta dai dati di prestazione in quel caso, con gli stessi livelli di ottimizzazione

è lecito attendersi un ulteriore guadagno di prestazione dall'esecuzione non bloccante del calcolo nel componente hardware custom

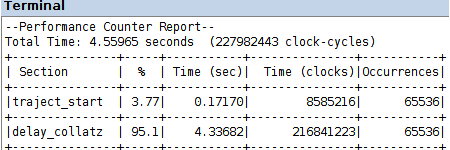

dai Performance Counter Report che seguono, a confronto con i dati analoghi della realizzazione con tutto il calcolo in software, risulta uno speed-up 21x con ottimizzazione di default O1 e 16x con ottimizzazione O3; i corrispondenti valori dello speed-up con accelerazione bloccante sono 15x con O1 e 13x con O3

materiali utili per l'esperienza di laboratorio proposta: