DMI – Graduate Course in Computer Science

Copyleft

![]() 2020 Giuseppe Scollo

2020 Giuseppe Scollo

this tutorial deals with:

development of a SoC with applications is a typical HW/SW codesign activity

the Quartus tool utilized in this lab tutorial for the integration of hardware components in SoC development is Qsys

the subsequent compilation in Quartus produces a system for the programming of the FPGA, whereupon one may load a software application by means of the Monitor Program, compile it and execute it under control of the GDB debugger, as shown in the previous lab tutorial

in this lab tutorial two simple Qsys design cases are shown:

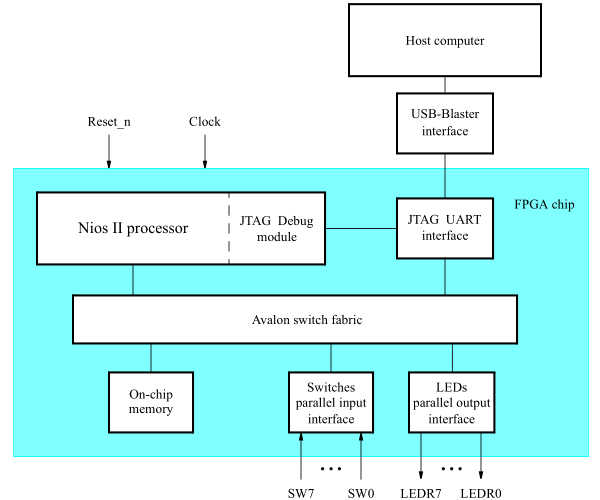

the first part of the classroom lab reproduces the execution of the example of Qsys construction of a Nios II system equipped with a small amount of on-chip memory and a couple of memory-mapped I/O peripherals with Avalon bus interfaces, as shown in the figure, described in the first reference tutorial

Figure 1. Block diagram of a simple example of Nios II system on FPGA

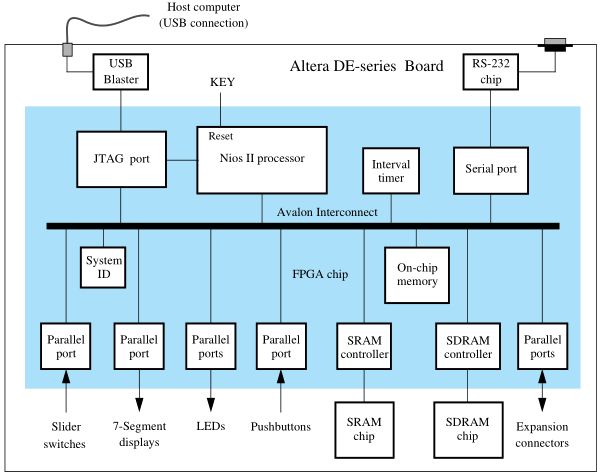

the second part of the classroom lab reproduces the execution of the example of construction of a Qsys system equipped with a memory-mapped custom hardware component with an Avalon bus interface, as shown in the figure, described in the second reference tutorial

Figure 2. Block diagram of a complex example of Nios II system on FPGA

recommended readings: