# Introduction to the combined use of Gezel with a VHDL simulator

Tuitorial Oil on Dedicated systems

Teacher: Giuseppe Scollo

University of Catania Department of Mathematics and Computer Science Graduate Course in Computer Science, 2018–19

DMI - Graduate Course in Computer Science

Copyleft @ 2019 Giuseppe Scollo

1 di 8

# Table of Contents

- 1. Introduction to the combined use of Gezel with a VHDL simulator

- 2. tutorial outline

- 3. hardware models in Gezel

- 4. example: Collatz trajectories

- 5. automated translation to VHDL and simulation

- 6. operational tips

- 7. references

DMI - Graduate Course in Computer Science

#### tutorial outline

this tutorial deals with:

- hardware models in Gezel: features, limitations, practical uses

- Gezel software installation

- > translation of Gezel models to VHDL models

- Quartus software installation

- compilation, analysis and tuning of VHDL models in Quartus

- > editing of testing waveforms in Quartus

- functional simulation in Quartus' ModelSim

DMI - Graduate Course in Computer Science

Copyleft @ 2019 Giuseppe Scollo

3 di 8

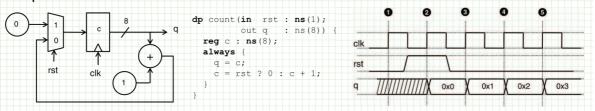

#### hardware models in Gezel

single-clock synchronous digital circuits, composed of an interconnection of:

- > combinational logic

- flip-flops

thus also including widely used components such as: registers, adders, multiplexers etc. abstraction level: clock cycles, RTL models

what *cannot* be modeled: asynchronous hardware, HW with latches, multi-phase clocked HW etc.

RTL models are adequate in a great deal of practical cases, viz. to describe hardware implementations of algorithms

## example:

Schaumont, Fig. 1.1 - Models and behaviour of a hardware component

DMI — Graduate Course in Computer Science

#### example: Collatz trajectories

reconsider the example seen in the first lecture:

```

x_0 \xrightarrow{16} 0 \xrightarrow{32} x \xrightarrow{x[1-31]} x[0]

start

x_0 \xrightarrow{16} 0 \xrightarrow{1} x \xrightarrow{x[1-31]} x[0]

x_0 \xrightarrow{16} 0 \xrightarrow{1} x \xrightarrow{x[1-31]} x[0]

```

what can be done with such a model?

e.g., how can one visualize its behaviour?

industrial development tools need descriptions in standard languages such as VHDL or Verilog ...

DMI - Graduate Course in Computer Science

Copyleft @ 2019 Giuseppe Scoll

5 di 8

#### automated translation to VHDL and simulation

the code generator of the Gezel platform yields a translation into *synthesizable* NHDL lab experience:

- 1. install the Gezel base software and its VHDL code generator

- 2. get the source file collatz.fdl containing the Gezel example description

- 3. run the translation from the command line: fdlvhd collatz.fdl

- 4. install Quartus Prime Lite 16.1 by Intel Corp., launch it, and then in this system:

- 5. create a new Quartus project named collatz

- 6. copy the .vhd files produced by step 3 into the project directory

- 7. assign the aforementioned files to the project and compile

- 8. check any error or warning messages

- 9. set the clock to a frequency that warrants a positive value for the worst-case slack

- create test waveforms for the collatz circuit, with clock input corresponding to the frequency established in the previous step and value 27 for the trajectory start

- 11. run the functional simulation

- 12. repeat the simulation for different trajectory starts

DMI - Graduate Course in Computer Science

#### operational tips

# a few tips to perform the lab experience on Ubuntu 16.04:

the following notes present a few workarounds to little troubles which otherwise may affect the execution of the lab experience

- installation on a newer version of the Ubuntu distribution may be tried; this requires recompilation of the Gezel sources, but it has not been tested; if the attempt fails, you may get the VHDL files produced by the Gezel code generator from the reserved lab area and run the experience starting from step 4

- on a different operating system you may install an Ubuntu virtual machine or otherwise get the VHDL files

and run the experience starting from step 4, as mentioned above

- · you may download the ZIP archive of all tips

- 1. Gezel installation tips for the VHDL code generator

- 2. Quartus Prime Lite 16.1 installation and startup tips on Ubuntu 16.04

- 3. Quartus project assignment tips

- 4. clock fine tuning tips using Quartus TimeQuest Analysis

- 5. tips on using Quartus ModelSim

DMI - Graduate Course in Computer Science

Copyleft @ 2019 Giuseppe Scollo

7 di 8

### references

#### recommended readings:

Schaumont (2012) Cap. 1, Sez. 1.1.1; App. A.1

Quartus Prime Introduction Using NHDL Designs - For Quartus Prime 16.1; Intel FPGA University Program Using TimeQuest Timing Analyzer - For Quartus Prime 16.1, Sect. 1-2, 4; Intel FPGA University Program Introduction to Simulation of VHDL Designs - For Quartus Prime 16.1; Intel FPGA University Program

for further consultation:

Schaumont (2012) App. A.2

other useful material for the proposed lab experience:

Gezel installation manual Quartus Prime Lite 16.1 download Intel FPGA University Program Installer

DMI — Graduate Course in Computer Science