DMI – Graduate Course in Computer Science

Copyleft

![]() 2018 Giuseppe Scollo

2018 Giuseppe Scollo

outline:

seminar by Grazia Pagano (PDF, in Italian)

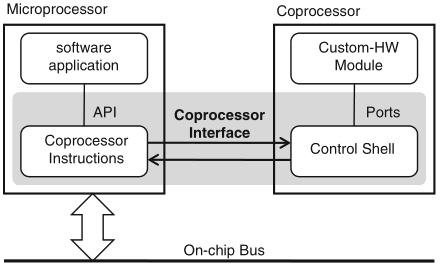

Schaumont, Figure 11.7 - Coprocessor interface

when high data-throughput between the software and the custom hardware is needed, a dedicated processor interface outperforms memory-mapped interfaces

both the coprocessor instruction set and the specific coprocessor interface depend on the type of processor—not all processors have a coprocessor interface

main advantages of a coprocessor interface over an on-chip bus:

the integration of hardware and software can be considerably accelerated as follows:

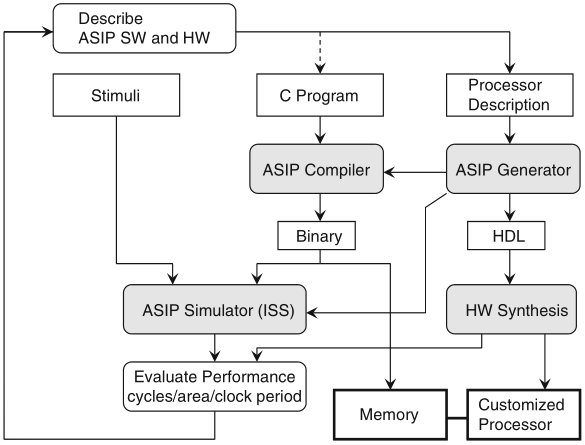

the resulting design is called an Application-Specific Instruction-set Processor (ASIP)

ASIP design automates some of the more difficult aspects of HW/SW codesign:

Schaumont, Figure 11.12 - ASIP design flow

sequential ASIP design does not generally deliver better performance than SoC design based on custom hardware modules, yet it does deliver less error-prone results

the Nios-II softcore processor has a coprocessor interface whereby custom instructions may be defined and hardware modules may be attached to

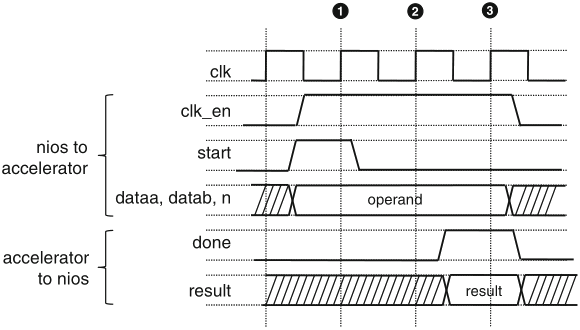

Schaumont, Figure 11.15 - Nios-II custom-instruction interface timing

the interface supports variable-length execution of custom instructions through a two-way handshake

the clk_en input is used to mask off the clock to the custom hardware when the instruction is inactive

the use of a local register file in the custom hardware module is also supported

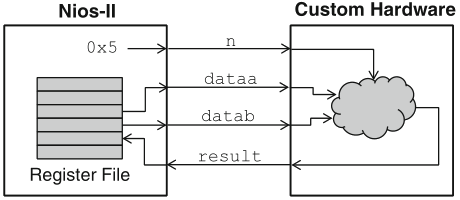

Schaumont, Figure 11.16a - Nios-II custom-instruction integration with processor register file

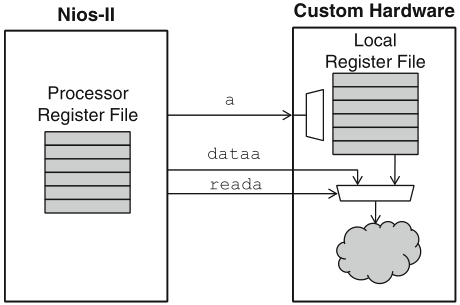

Schaumont, Figure 11.16b - Nios-II custom-instruction integration with local register file

a custom instruction may take operands from either register file: registers prefixed with r are located in the processor, while registers prefixed with c are located in the custom hardware

figure 11.16b shows the case for the first input operand only: the control signal reada selects either the processor's or the local register file

recommended readings:

for further consultation: