DMI – Graduate Course in Computer Science

Copyleft

![]() 2018 Giuseppe Scollo

2018 Giuseppe Scollo

outline:

SoC: a domain-specialized platform on a single chip

domain examples:

video-processing application examples:

advantages of domain specialization:

four orthogonal dimensions of analysis of the organization and interplay of components in a SoC:

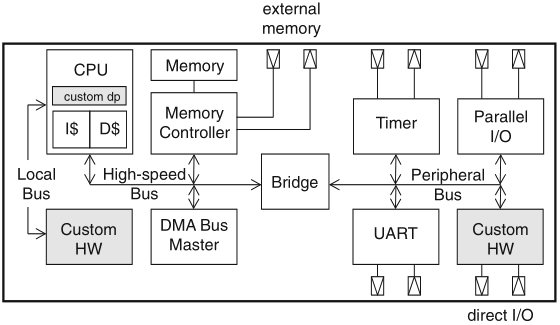

Schaumont, Figure 8.1 - Generic template for a system-on-chip

in this generic architecture:

shaded blocks in fig. 8.1 show three ways to attach custom hardware in a SoC context

in SoC design, there is no single best way to integrate hardware and software

factors to trade-off in SoC design include:

four design principles for any SoC:

hardware heterogeneity : FSMDs, microprogrammed engines, RISC microprocessors

task-level parallelism is possible in a SoC thanks to their multiplicity

functional heterogeneity : computationally different units

thanks to parallelism at all levels a SoC can fully exploit the hardware technology, in two respects:

multiple bus segments using bus bridges may prevent the central bus bottleneck

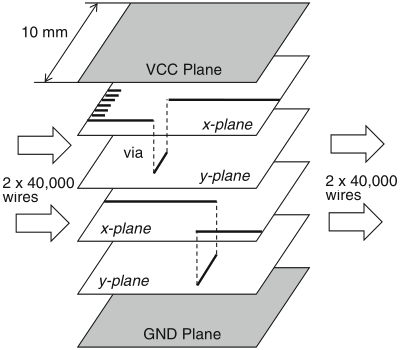

Schaumont, Figure 8.2 - Demonstration of the routing density in a six-layer metal 90 nm CMOS chip

an example by Tensilica founder Chris Rowen about extremely high bandwidth of on-chip communication:

assumptions:

→ a theoretical bandwidth of 40 Tbps!

off-chip communication is orders of magnitude below

heterogeneity of silicon-based memories in a SoC is summarized in Table 8.1

| Type |

Register Register file |

DRAM |

SRAM |

NVROM (ROM, PROM, EPROM) |

NVRAM (Flash, EEPROM) |

| Cell size (bit) | 10 transistors | 1 transistor | 4 transistors | 1 transistor | 1 transistor |

| Retention | 0 | Tens of ms | 0 | ∞ | 10 years |

| Addressing | Implicit | Multiplexed | Non-muxed | Non-muxed | Non-muxed |

| Access time | < 1 ns | < 20 ns | < 10 ns | 20 ns | 20 ns (read) 100 μs (write) |

| Power consumption | High | Low | High | Very low | Very low |

| Write durability | ∞ | ∞ | ∞ | ∞ | One million times |

Schaumont, Table 8.1 - Types of memories

distributed storage significantly complicates the concept of a centralized memory address space, when data need to be shared among components

a control hierarchy among components ensures that the entire SoC operates as a single logical entity

local control may be played by dedicated components, such as coprocessors or other custom hardware, but their operations and those of the central controller are not entirely independent

the design of a good control hierarchy is a challenging problem

depending on the workload distribution, any component may cause a system bottleneck–the challenge for the SoC designer (or platform programmer) is to be aware of the location of such system bottlenecks, and to control them

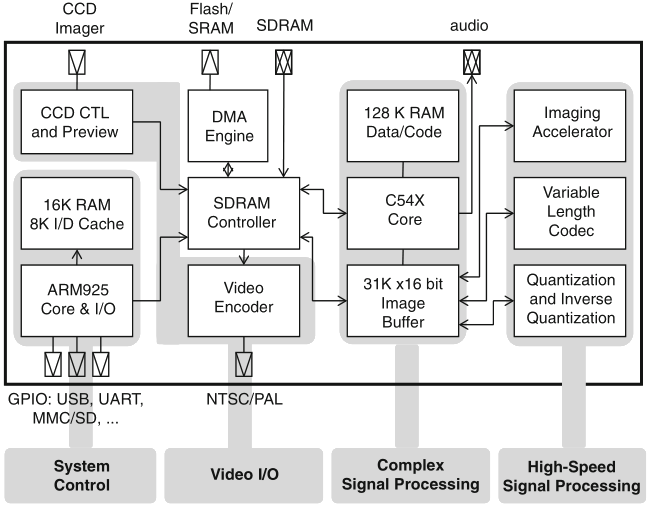

real case study: a digital media processor by Texas Instruments

Schaumont, Figure 8.3- Block diagram of portable multi-media system

several device modes, including:

four specialized subsystems are shaded in figure 8.3, centered around the SDRAM controller which organizes the traffic to the large, off-chip memory holding image data

the previously discussed four properties can be recognized in this chip: