DMI – Graduate Course in Computer Science

Copyleft

![]() 2018 Giuseppe Scollo

2018 Giuseppe Scollo

outline:

FSM models are well suited to capture the control flow and decision making of algorithms, however, they lack hierarchy; this gives rise to severe limitations when dealing with complex control systems

state explosion

exception handling

runtime flexibility

a more flexible control is obtained by microprogramming it

the first idea of microprogramming was proposed by Maurice Wilkes, in 1951, but it found wide application starting from the sixties, to become dominant in the subsequent decade with the diffusion of CISC architectures (Complex Instruction-Set Computer)

starting from the eighties, RISC architectures (Reduced Instruction-Set Computer) have competed with CISC ones, to become dominant eventually

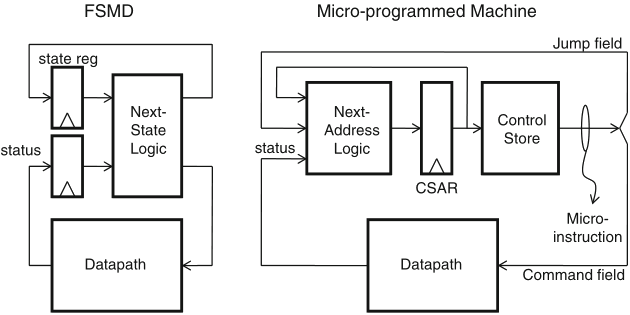

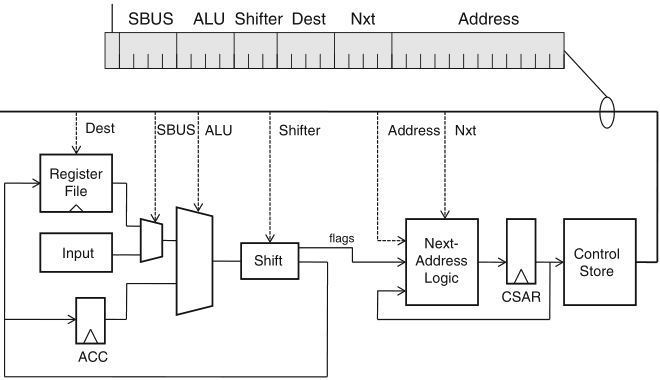

Schaumont, Figure 6.3 - In contrast to FSM-based control, microprogramming uses a flexible control scheme

CSAR (Control Store Address Register): analogue of the conventional Program Counter

microprogrammed control solves the problems of FSMs:

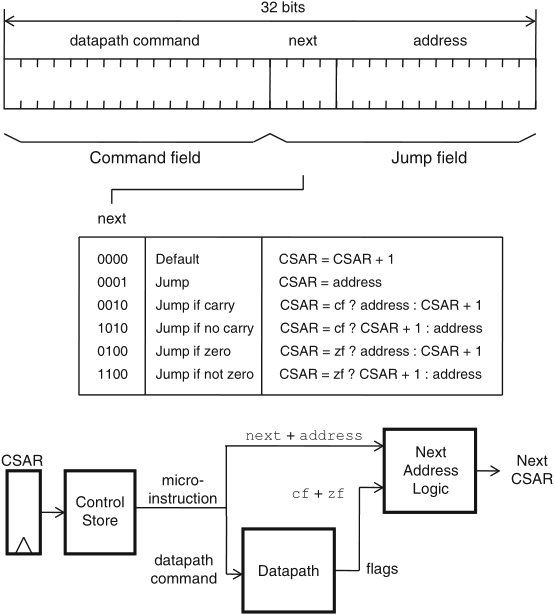

Schaumont, Figure 6.4 - Sample format for a 32-bit

micro-instruction word

microinstruction format and encoding is driven by design trade-offs; a sample encoding is as follows

the format in figure 6.4 is not optimal, as the address field is only used for jump instructions–it may be used for other purposes with other instructions

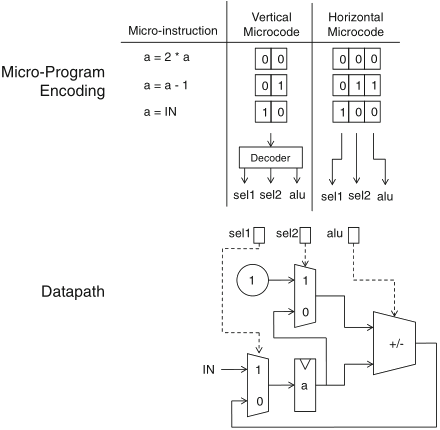

Schaumont, Figure 6.5 - Example of vertical versus horizontal

micro-programming

another space-time trade-off is presented by the alternative for the command field:

a combined solution is often adopted, e.g. the encoding in the next field:

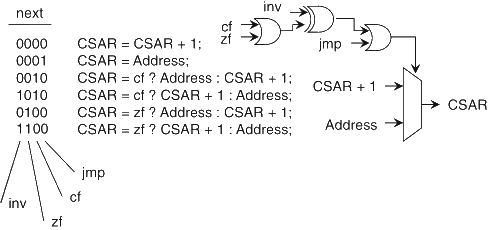

Schaumont, Figure 6.6 - CSAR encoding

the datapath of a microprogrammed machine consists of three elements:

each of these elements may contribute a few control bits to the microinstruction word, for example:

the datapath may also generate status flags for the microprogrammed controller

here is an example of microprogrammed control of a datapath that includes: an ALU with shifter unit, a register file with eight entries, an accumulator register, and an input port

mixed horizontal/vertical encoding: overall horizontal, for each unit in the datapath takes a distinct portion of the control word, vertical encoding of each unit control signals in that portion

Schaumont, Figure 6.7 - A micro-programmed datapath

the shifter also generates flags, which are used by the microprogrammed controller to implement conditional jumps

control word fields:

the datapath fetches and executes a microinstruction every clock cycle

table 6.1 presents an example of microinstruction encoding for the given architecture (first part):

| Field | Width | Encoding | |||

| SBUS | 4 | Selects the operand that will drive the S-Bus | |||

| 0000 | R0 | 0101 | R5 | ||

| 0001 | R1 | 0110 | R6 | ||

| 0010 | R2 | 0111 | R7 | ||

| 0011 | R3 | 1000 | Input | ||

| 0100 | R4 | 1001 | Address/Constant | ||

| ALU | 4 | Selects the operation performed by the ALU | |||

| 0000 | ACC | 0110 | ACC | S-Bus | ||

| 0001 | S-Bus | 0111 | not S-Bus | ||

| 0010 | ACC + S-Bus | 1000 | S-Bus + 1 | ||

| 0011 | ACC – S-Bus | 1001 | ACC + 1 | ||

| 0100 | S-Bus – ACC | 1010 | 0 | ||

| 0101 | ACC & S-Bus | 1011 | 1 | ||

table 6.1 (second part):

| Field | Width | Encoding | |||

|

| |||||

| Shifter | 3 | Selects the function of the programmable shifter | |||

| 000 | logical SHL(ALU) | 100 | arith SHL(ALU) | ||

| 001 | logical SHR(ALU) | 101 | arith SHR(ALU) | ||

| 010 | rotate left ALU | 111 | ALU | ||

| 011 | rotate right ALU | ||||

| Dest | 4 | Selects the target that will store S-Bus | |||

| 0000 | R0 | 0101 | R5 | ||

| 0001 | R1 | 0110 | R6 | ||

| 0010 | R2 | 0111 | R7 | ||

| 0011 | R3 | 1000 | ACC | ||

| 0100 | R4 | 1111 | unconnected | ||

| Nxt | 4 | Selects next-value for CSAR | |||

| 0000 | CSAR + 1 | 1010 | cf ? CSAR + 1 : Address | ||

| 0001 | Address | 0100 | zf ? Address : CSAR + 1 | ||

| 0010 | cf ? Address : CSAR + 1 | 1100 | zf ? CSAR + 1 : Address | ||

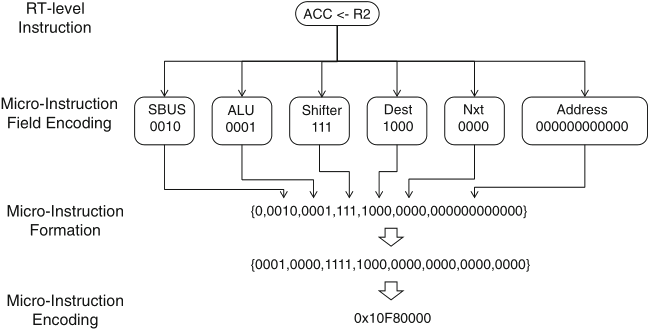

using the encoding defined in table 6.1, a microinstruction is formed by selecting a function for each module in the datapath and a next address for the Address field (with a suitable don't care value for this whenever Nxt is null)

by way of example, let's see how an RTL instruction, such as ACC ← R2, is translated to a microinstruction

Schaumont, Figure 6.8 - Forming micro-instructions from register-transfer instructions

complex control operations, such as loops and if-then-else statements, can be expressed as a combination (or sequence) of RTL instructions

the microprogram is written in a symbolic RTL notation that immediately translates to microinstructions in a similar way as in the previous example

| Command Field | || | Jump Field | |

| IN → R0 | |||

| IN → ACC | |||

| Lcheck: | (R0 – ACC) | || | JUMP_IF_Z Ldone |

| (R0 – ACC) << 1 | || | JUMP_IF_C Lsmall | |

| (R0 – ACC) → R0 | || | JUMP Lcheck | |

| Lsmall: | ACC – R0 → ACC | || | JUMP Lcheck |

| Ldone: | JUMP Ldone | ||

Schaumont, Listing 6.1 - Micro-program to evaluate a GCD

recommended readings:

for further consultation: