DMI – Graduate Course in Computer Science

Copyleft

![]() 2018 Giuseppe Scollo

2018 Giuseppe Scollo

this tutorial deals with:

development of a SoC with applications is a typical HW/SW codesign activity

the Quartus tool utilized in this lab tutorial for the integration of hardware components in SoC development is Qsys

a slightly more complex example is the subject of the present tutorial:

profiling a program: measuring the time spent in different parts of the program, to identify those which are critical to execution speed

three tools considered in (fairly dated) document Profiling Nios II Systems :

the third method is utilized here, since it yields the best accuracy and the easiest use within the program, while the aforementioned upperbound is no problem for the application at stake

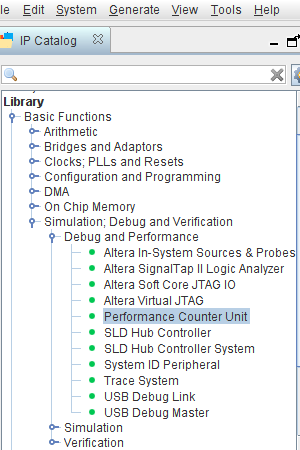

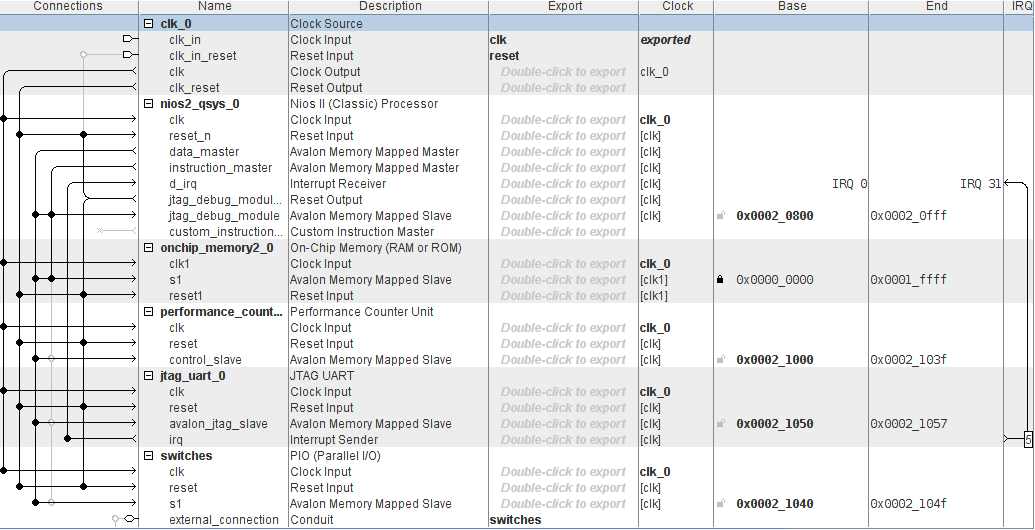

the figure displays the Qsys contents of the Nios II system with Performance Counter Unit

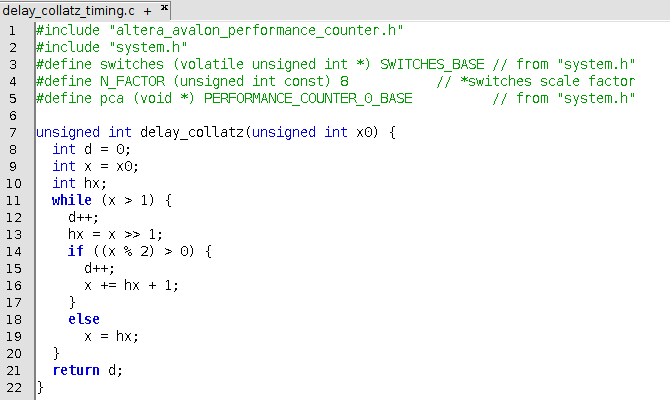

the C function in the figure is a software implementation of the delay computation of a Collatz trajectory with given start point

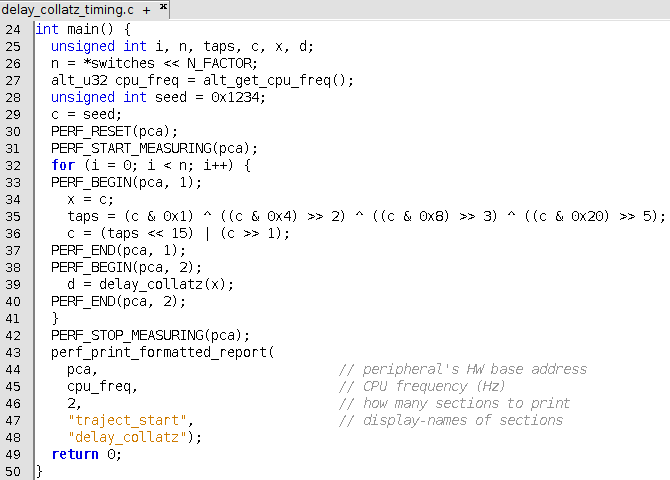

unlike the previous lab experiences relating to hardware implementations of the subject function, the user input here determines the length of the sequence of trajectories to be generated in the main program, that is the number of function invocations

the preprocessing directives, previously shown, enable the use of the performance counter API as well as of other symbols (SWITCHES_BASE in this case) defined in the software interface of the system built with Qsys

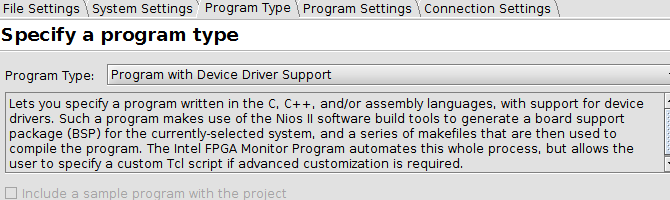

the interface is provided by the BSP, whose construction here is automated by the Monitor Program, following the choice of program type Program with Device Driver Support

other aspects of the BSP (e.g. compiler or linker options) may be specified by providing a custom Tcl script

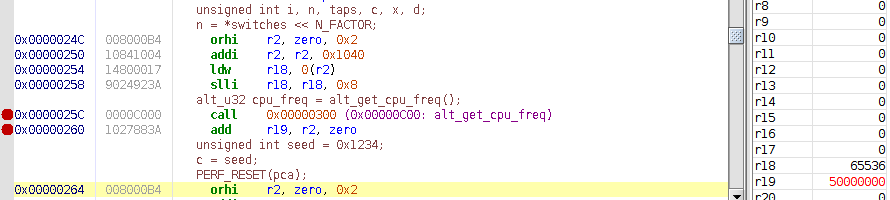

C source-level debugging is also available in the Monitor Program (visualization of values of variables)

the program disassembly remains accessible anyway, where to set breakpoints and to examine its execution status at critical points for correctness verification

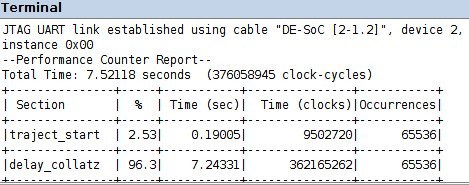

after removal of all breakpoints, system reset and execution restart, the profiling module generates the performance report displayed in the figure

the proposal aims at the design and implementation of a HW/SW system with similar structure and features as those of the example presented in this tutorial, using the same development and profiling tools, but for a different application; precisely, the work goes about:

recommended readings:

readings for further consultation:

useful materials for the proposed lab experience: