DMI – Graduate Course in Computer Science

Copyleft

![]() 2016-2017 Giuseppe Scollo

2016-2017 Giuseppe Scollo

this tutorial deals with:

precursors: PLA, PAL, CPLD

typical FPGA constituents:

Wilson, Fig. 2.3 - FPGA complex logic block

configuration of the CLB in the figure:

typical work sequence (not all steps are present in every design):

physical synthesis, which is automated by several analysis and optimization tools, is composed of various processes:

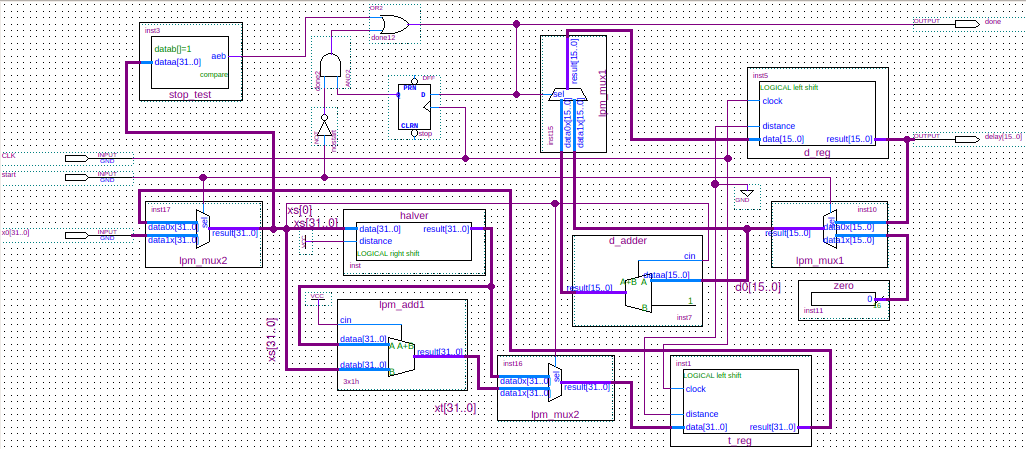

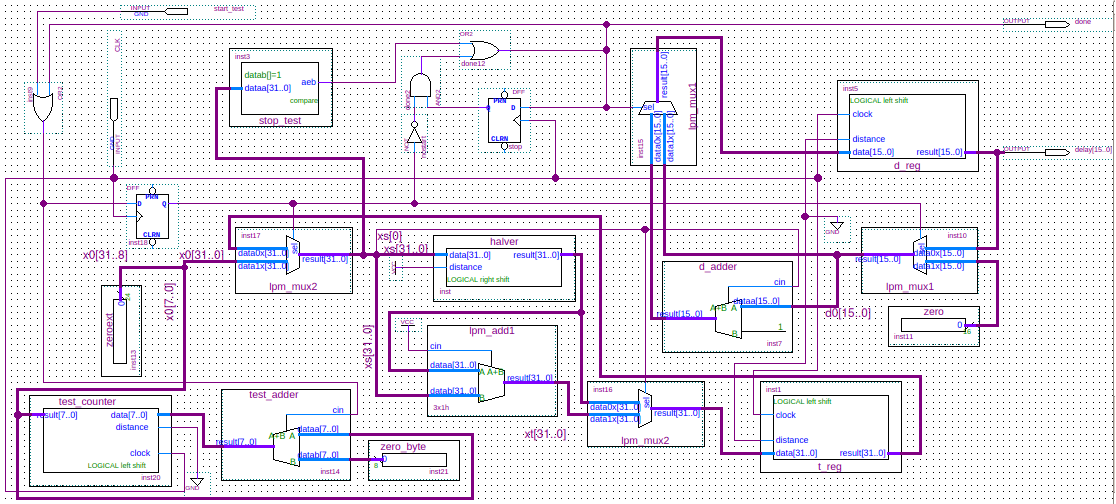

it is possible to describe, simulate and synthesize hardware circuit models also without making use of an HDL, when a graphical editor is available for schematic design, together with adequate software tools

schematic using library parameterized modules (lpm)

a testbench for the Collatz delay datapath

recommended readings:

useful materials for the proposed lab experience (source: Altera University Program, 2014)